Introduction to VLSI Systems

Background:

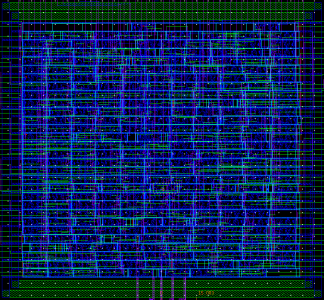

From the invention of the first simple Integrated-circuit by Jack Kilby and Robert Noyce in late 1950s, to the 5.5 billion transistors in the latest Xeon processors, the rate of growth for Very Large Scale Integrated (VLSI) Systems is unparalleled for any technology.

This course will serve as an introductory course covering different design aspects of digital CMOS circuits. The lecture topics will be geared towards developing an understanding of how digital ICs are designed using static and dynamic CMOS technologies. The class projects will be geared towards getting an extensive experience with industry-standard computer-aided design (CAD) tools, including the use of a 45 nm Physical Design Kit, Cadence Schematic and Layout Editor (Virtuoso), Mentor Graphics Calibre DRC and LVS, and Synopsys Design Compiler.

Objectives:

- Understand how to analyze the worst-case high-to-low and low-to-high switching times of a static CMOS gate.

- Design combinational and sequential circuits and characterize timing and power using the industry-standard CAD tools.

- Design large circuits comprised of these combinational gates and sequential blocks, characterize its timing and power, and analyze tradeoffs.

- Design logical functions in a wide variety of CMOS technologies.

- Layout standard cells.

- Understand the details of memory elements, including SRAM and DRAM

Broad Contents:

- System Verilog

- Introduction to VLSI

- MOSFET device properties

- CMOS inverter design

- Static combinational logic circuits

- Standard cells design and layout

- Memory element (latch and flip-flop) design

- Logic families such as dynamic, domino, pseudo-NMOS/PMOS, switch

- Parasitics, interconnect, skew

- Synchronous logic and timing analysis

- Memory, including SRAM, DRAM, CAM, FLASH

- Power, scaling, and industry trends

Suggested Reading:

- Weste & Harris, CMOS VLSI Design: A Circuits and Systems Perspective, 4th ed., Addison-Wesley, 2010.

- Rabaey, Chandrakasan, and Nikolic, Digital Integrated Circuits, A Design Perspective, 2nd ed., Prentice-Hall, 2003.

- Uyemura, CMOS Logic Circuit Design, Kluwer Academic Publishers, 2001.

Prerequisites:

- EECE 353

Course Structure [2017W1]:

- ~4 hours of lecture per week (Tues & Thurs 2-3:20pm @ tbd, Wed 11-11:50 @ tbd)

- 1 hour of tutorial focused towards Verilog and VLSI CAD tools [first two weeks], then towards problem solving (Wed 10-10:50 @ FSC-1003 or MCLD 348/358)

- A major project – broken down into smaller mini-projects. A written report is required for each mini-project.

Grading:

- Midterm 20%

- Projects & Reports 50%

- Final 30%

Instructor’s Office Hour:

- Tuesdays 4:00-5:00pm K4017

- After Lectures

- By appointment

FAQs:

Q. I do not have much experience with CMOS circuits. Can I still register for this course?

Yes, if you satisfy the pre-requisite condition. Basics of CMOS would be covered in this course.

Q. Would I be learning Verilog in this course?

It is assumed that you have extensive experience with VHDL from your pre-requisite. Basics of Verilog, and the differences between VHDL and Verilog would be covered in this course. The first two mini-projects would be based on Verilog.

Q. What are the tutorials for?

The first two tutorials are on Verilog. A significant number of tutorials later in the course are on the tools. We would first provide tutorial documents on Cadence, Synopsys and Mentor Graphics to you. They include step-by-step instructions for simulation/layout. Overview of these documentation will be provided in the tutorials, and we will answer any specific questions. As there are no homework assignments in the course, tutorials before the mid-term and final exams would be used for solving example-problems.

Q. Do I have to attend the tutorials?

No, they are not mandatory, but are strongly recommended. All the tutorial content would be provided to you as handouts. We are currently looking into also making videos for the CAD-related tutorials.