Integrated Circuits for Phase-Locked Loops

Background:

Phase-locked loops (PLLs) are used in almost every system-on-chip – microprocessor, radio-frequency ICs, high-speed I/Os links etc. – to provide the clock frequency. The performance of the SoC is severely impacted by the signal integrity of the clock. Therefore, the design of the PLL is significantly challenging. A PLL designer needs to have an understanding of the system specifications such as jitter and phase noise, spurious emissions, power supply sensitivity, etc. This demands a knowledge of analog circuits, digital circuits, mixed-signal circuits, and control systems. In this introductory course on PLLs, students will learn those concepts and obtain the ability to implement, validate and assess them.

Objectives:

- Obtain an understanding of a variety of system-level trade-offs in PLLs.

- Be able to design and simulate both analog and digital PLLs using Cadence, CppSim and MATLAB tools.

- Obtain an overview of the current literature in PLLs.

Broad Contents:

- Introduction to PLLs

- Types and orders of PLL

- Noise and Jitter

- Integer and fractional frequency synthesizers

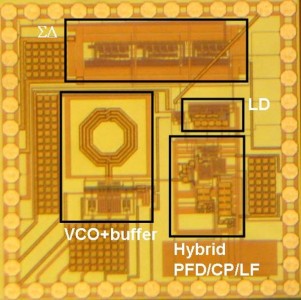

- Design of different PLL circuits such as phase-frequency detectors, subsampling detectors, time to digital converters, loop filters, charge pumps, voltage and digitally controlled oscillators, frequency dividers, sigma-delta modulators

Suggested Reading:

There is no single textbook that covers the course topics as taught. The course will be taught using the instructor’s lecture notes, along with reference books and IEEE Journals (JSSC, TCAS) and Conferences (ISSCC, VLSI Symposium, CICC).

Reference Textbooks:

- Phase Locked Loops 6/e: Design, Simulation, and Applications, Roland Best, McGraw Hill, 2007 (6th Ed).

- Integrated Circuit Design for High-Speed Frequency Synthesis, John Rogers, Calvin Plett, Foster Dai, Artech House, 2006.

- Phaselock Techniques, F. Gardner, John Wiley & Sons, 2005.

- All-Digital Frequency Synthesizer in Deep-Submicron CMOS, Robert B. Staszewski and Poras T. Balsara, Wiley, 2006.

- Design of CMOS Phase-Locked Loops, Behzad Razavi, Cambridge, 2020.

Prerequisites:

- Anyone of ELEC 401, 402, 403, 404, 501, 503, 504, 506

Course Structure:

- Two major projects – broken down into smaller mini-projects. A written report is required for each mini-project.

- 3 hours/week of Classroom time

- Ad-hoc tutorials

- Content delivery, Q/As – through Piazza and YouTube.

Grading:

- Projects & Reports 70%

- Exam 20%

- Quizzes 10%

Instructor’s Office Hour:

- TBD

- After Lectures

- By appointment

FAQs:

Q. I do not have much experience with CMOS circuits. Can I still register for this course?

Yes, if you satisfy the pre-requisite condition.

Q. What do you recommend for revising the basics of Analog CMOS Design?

I would suggest reading and becoming comfortable with Chapter 3 “Basic Current Mirrors and Single-Stage Amplifiers” of Johns & Martin’s Analog Integrated Circuit Design textbook.

Q. I have not used Cadence Spectre before. What should I do?

We would provide tutorial documents on Cadence to you. They include step-by-step instructions for simulating basic circuits. You would need to learn them on your own. You may ask the instructor or other students if you have specific questions.